僗僷僀僗丂丂慻傒崬傒惂屼憰抲偺庴拲惢嶌

彫婯柾慻傒崬傒憰抲偵岦偄偨CPLD

暯惉26擭 8寧 30擔

丂CPLD偺撪晹峔惉

丂CPLD偺撪晹峔惉偼戝偒偔2偮偵暘偐傟傑偡丅摿偵柤慜偑偁傞栿偱偼側偄偺偱偡偑丄偙偙偱偼廬棃宆偲FPGA椶帡宆偲屇傇偙偲偵偟傑偡丅

丂丂丂丂廬棃宆CPLD

丂廬棃宆CPLD偼偦偺慜恎偱偁傞PLD夞楬偺婎杮峔惉傪摜廝偟偰偄傑偡丅婎杮揑偵偼AND丒OR丒INVERT偺慻傒崌傢偣亄D FF偱慡偰偺榑棟夞楬傪峔惉偟傑偡丅尰峴惢昳偱偼僓僀儕儞僋僗幮偺XC9500XL偍傛傃Cool Runner丄傾儖僥儔幮偺MAX3000A偑奩摉偟傑偡丅

偙偺僞僀僾偼儅僋儘僙儖偲屇偽傟傞懡擖椡丒懡弌椡偺婡擻僽儘僢僋傪暋悢屄幚憰偟偰偄傑偡丅

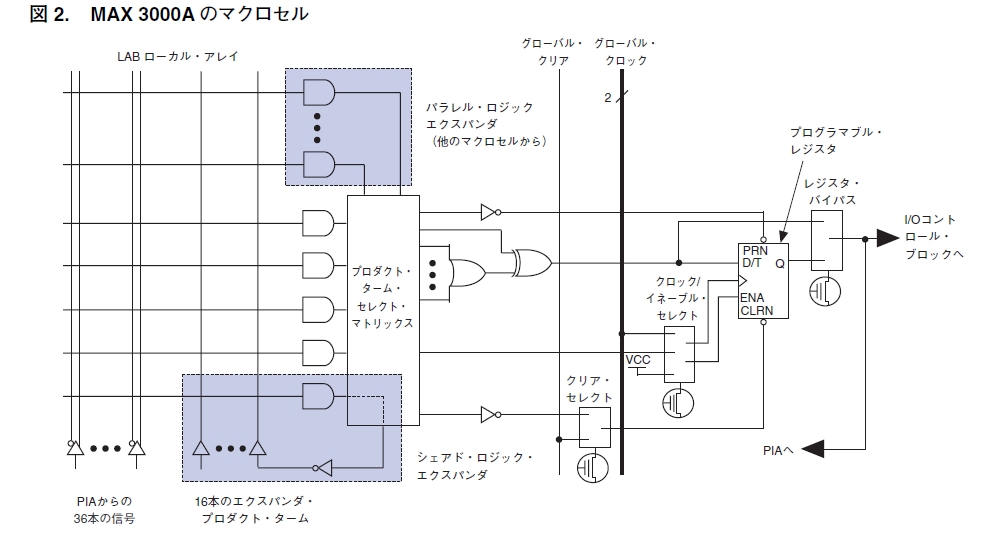

埲壓偵廬棃宆CPLD偺婡擻僽儘僢僋恾傪堷梡偟傑偡丅乮MAX 3000A 僾儘僌儔儅僽儖丒儘僕僢僋丒僨僶僀僗丒僼傽儈儕丒僨乕僞僔乕僩傛傝堷梡乯

丂偙偺恾偺尒曽偼擄偟偄偺偱偡偑丄堦偮偺儅僋儘僙儖偵偼崌寁偱乮36亄16乯52杮偺擖椡傪帩偪丄16杮偺弌椡傪帩偭偰偄傑偡丅偙傟埲忋偺擖椡偑昁梫側偲偒偼椬偺儅僋儘僙儖偐傜怣崋偺堦晹傪庁梡偱偒傞乮忋婰偺16杮偑偦傟乯傛偆偵側偭偰偄傑偡丅偙偺婡擻偵傛偭偰幚嵺偵偼旕忢偵懡偔偺擖椡傪張棟偱偒傞帠偵側偭偰偼偄傑偡丅偙偙傑偱偺悢帤偼傾儖僥儔幮偺MAX3000A偱偺傕偺偱偡丅僓僀儕儞僋僗幮偺惢昳偱偼懡彮堘偭偰偄傑偡乮偑戝偒側堘偄偱偼偁傝傑偣傫乯丅

丂丂丂丂FPGA椶帡宆

丂偙偪傜偼媽棃偺暘椶曽朄偱偼CPLD偵偼暘椶偱偒側偄僞僀僾偱偡丅撪晹夞楬偺婎杮偼FPGA偱巊梡偝傟傞儘僕僢僋僄儗儊儞僩偲屇偽傟傞婡擻僽儘僢僋傪懡悢幚憰偡傞偙偲偱幚尰偟偰偄傑偡丅傾儖僥儔幮偺MAX嘦埲崀偺僨僶僀僗偑奩摉偟傑偡丅

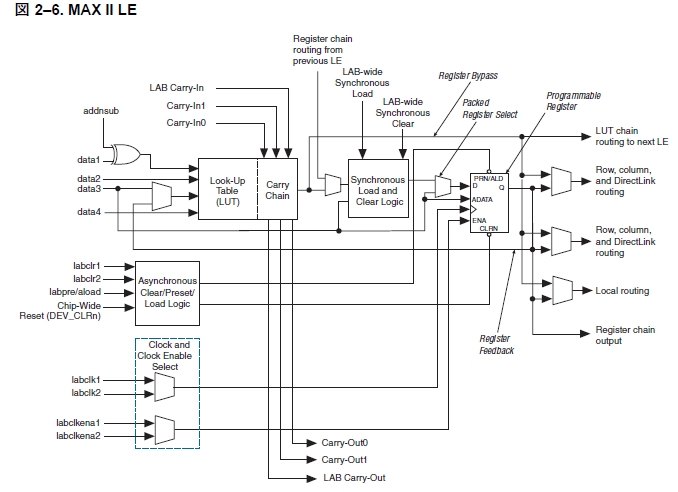

偙偪傜偼4擖椡傪婎杮偵壗捠傝偐偺弌椡偑壜擻側傛偆偱偡丅壓婰偵傾儖僥儔幮偺MAX嘦偺儘僕僢僋僄儗儊儞僩偺婡擻僽儘僢僋恾傪堷梡偟傑偡乮MAX嘦僨僶僀僗僴儞僪僽僢僋傛傝堷梡乯丅

丂儅僋儘僙儖偲偺戝偒側堘偄偼婡擻僽儘僢僋偑旕忢偵彫偝側扨埵偲側偭偰偍傝丄僨僶僀僗撪晹偺儗僀傾僂僩偵懳偡傞帺桼搙偑崅偄揰偱偡丅偦偺暘僨僶僀僗偺僼傿僢僥僀儞僌乮僨僶僀僗撪晹偺儗僀傾僂僩偺寛掕乯偵戝偒側晧扴偑妡偐傝傑偡丅摉弶偺PLD偑廬棃宆CPLD偺傛偆側峔惉傪偲偭偨偺傕夞楬偺幚憰抜奒偱偺僜僼僩僂僃傾偺晧扴傪寉偔弌棃傞偙偲傕梫場偱偁偭偨傠偆偲巚偄傑偡丅