令和元年 11月

アナログ入出力

発注したDA変換回路基板が届いたので、実装と初期評価を行います。

最初に行うのは、電源部の初期評価です。

4.DA変換基板の電源回路検証

電源回路には少し不安があります。使用したリニアレギュレータ78L15/79L12は開発時期が随分と古いため、今時の高分解能アナログ電源としては性能的に不足する心配があります。当初の目標は12ビットのADコンバータで10ビット程度の有効ビットが取れることでした。この程度なら問題ないだろうと使用したのですが、データシートの記載内容も十分ではない上、データシートに記載されているスペック自体もDC/DC電源と左程変わらないのが気掛かりです。

大体、この手の心配事は基板の発注が終わって一段落した頃に気が付くというのがお決まりです。その前までは基板設計に手一杯で、設計に立ち戻って考えるだけの余裕がないので無理もないのですが。

取り合えず、78L15/79L12では性能不足だったときの対応策として考えたのが以下です。

・ ICのピン互換品で低ノイズ品があれば交換する。

・ レギュレータの前後にノイズフィルタを追加して使えるレベルまでノイズを減らす。

・ 高精度アナログ用の超低ノイズレギュレータを使用する。

超低ノイズレギュレータはAD変換基板で使用する心算でいます。AD変換は変換器として16ビット品を使用するので電源部もそれなりの性能がないと折角の高性能が無意味になってしまう。本来の目的をを達成するだけなら必要は無いと思うのですが、追加費用に見合う程度の性能向上が期待できるなら最初くらいはトライしてみようと考えています。

ここでは、まず今の基板で評価できる方法を考えます。まずは互換品です。代わりのレギュレータとして使えそうな物を探します。

同一パッケージでは+側も−側も使えるものはありません。+側電源として面実装のSOT-89-3でならTorex社のXC6701DF02がありました。SOT-89-3は少し無理をすればTO95の穴位置に収まります。−側は残念ながら使えそうなものがありません。

こちらは実現は無理そうです。

次の方法として、ノイズフィルタの追加を考えます。候補として考えられるのはLCフィルタとフェライトビーズです。

性能目標としては、100kHzで20dB程度のPSRRを追加できれば十分でしょう。Lもフェライトビーズも周波数の上昇に比例してインピーダンスが上昇するのでパスコンとローパスフィルタを構成して、高周波のノイズ除去を期待できます。

注意すべきはLの周波数特性で物によるものの数MHzまでしかLとして機能しないものもあります。総じて小型の部品では周波数特性の上限が低い傾向にあります。フェライトビーズは逆で数百k〜数MHzである程度のインダクタンスを得られるものが必要です。多くのフェライトビーズはもう少し上の100MHz以上で最大のインダクタンスになるものが多く、数MHz以下の低い周波数帯でもある程度のインダクタンスを確保できる製品は限られます。村田製作所製ではRKシリーズが該当します。

ここまで準備をした段階で基板が上がってきたので、組み立てして電源のノイズレベルを測定します。

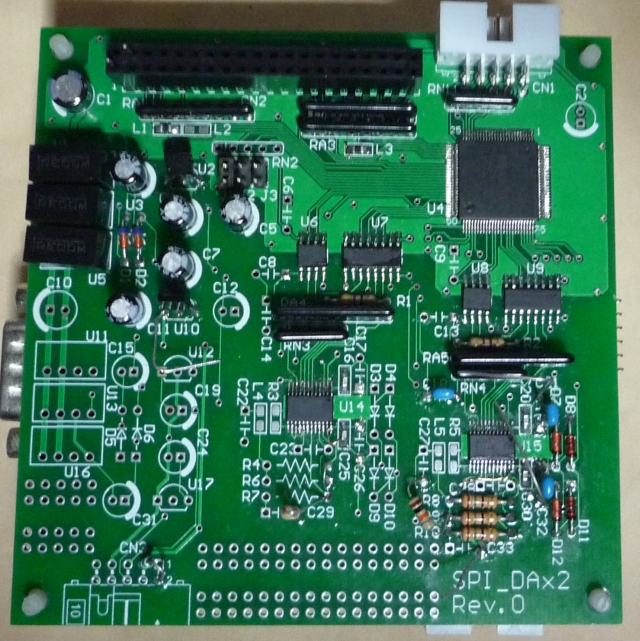

まずは実験基板の外観を図1.に示します。実験段階のため全ての部品を実装していません。必要な部品のみが実装されています。

写真では分かりづらいですが、mV単位のノイズレベルを測定するため基板の各所にグランドポストを立ててあります。

図1. SPI_DA基板の外観

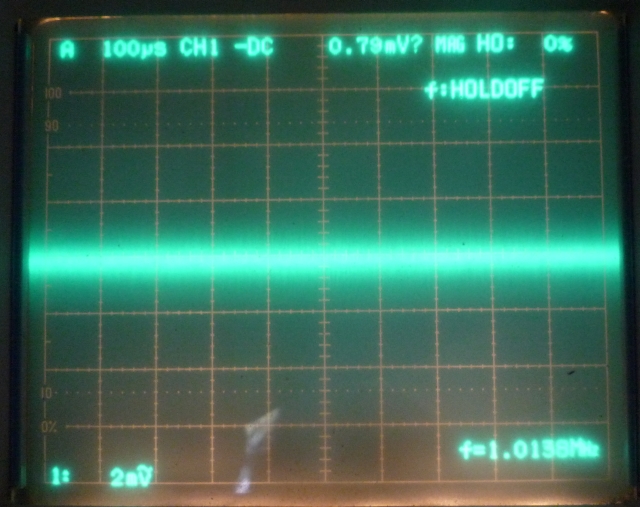

このときのDA出力信号のノイズレベルを図2.に示します。思ったよりも良い状態です。これなら目標はクリアできそうです。

電流出力についても同様の方法で確認してあります。

図2. 出力信号のノイズレベル

4.2 DA変換基板の変更予定

今回は回路図に記入漏れがありDAコンバータICの信号線が1本抜けてしまっているため、基板を作り直しします。

どうせ変更するなら以下の点についても修正を行います。

・ グランド周辺のパターン見直し、特にアナログ回路部のグランドパターンをベタパターンとしてグランド電位の差を小さくする。

・ DCDC電源のノイズレベルが大きい場合の対策用に電源部へフェライトビーズを追加実装できるように回路を変更する。

・ DAコンバータICのDVDD(デジタル電源)を5Vから3.3Vに下げることでDAコンバータICに混入するデジタルノイズを下げる。

これらの作業と平行してAD変換基板の準備も進めています。

次はAD変換について検討していきます。