令和元年 11月

アナログ入出力

DA変換基板の評価の続き

修正したDA変換基板が上がってきました。

一緒に発注したAD変換基板も上がっているのですが、こちらは発注した部品がまだ届いていないので、先にDA変換基板を実装します。

6.修正版DA変換基板

前回の基板との変更点は、下記になります。

・ 回路図の記入ミスによる配線漏れの修正

・ GNDラインをベタ面として特にアナログ部のGND電位差の影響を小さくする

・ DCDC電源部にノイズ対策用のフェライトビーズを追加する。

・ DAコンバータのデジタル電源を5Vから3.3Vに下げることで通信部からのデジタルノイズの影響を小さくする。

配線の追加以外の変更は効果がさほど無かったとしても、周囲環境に対する耐性という意味ではプラスに働くので、そのまま実装します。

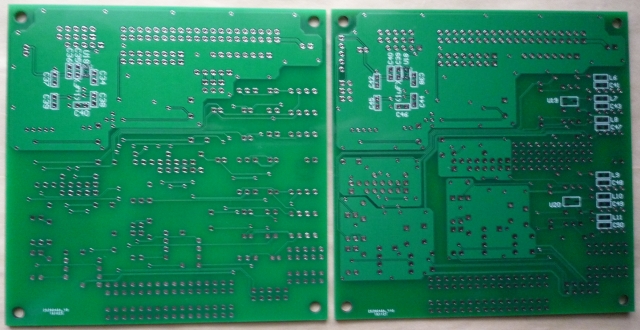

基板の修正前と修正後の裏面写真を図1.に示します。

図1.基板の修正前後の様子(左側が修正前、右側が修正後)

基板の中央部と左側付近に4個のベタ面があります。上下で1CH分の出力で、上側がデジタルGND、下側がアナログGNDのベタ面です。

右側に追加されている部品は電源部のフェライト・コンデンサおよびDAコンバータ用の3.3V電源です。

従来は細い配線であったものがベタ面となっており、アナログ部のGNDが強化されていることが分かると思います。

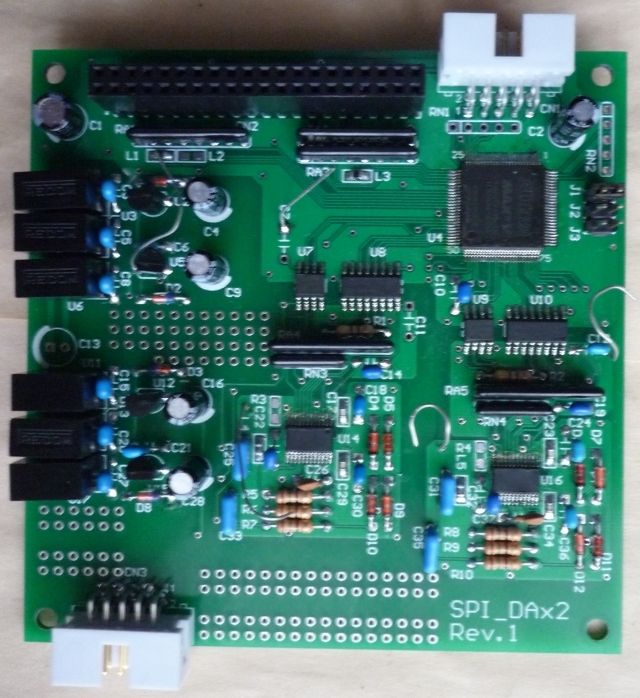

図2.は実装した基板の外観です。ここでもノイズレベルを正確に測定するためのGNDポストを各所に追加してあります。

GNDポストというとカッコいいですが単なるハリガネ(リード抵抗の切れ端)です。

図2.DA変換基板の外観

実装後、基本動作の確認を終わらせ、次に気になるのは出力のノイズレベルです。実測の結果を図3.に示します。

図3.DA変換の出力に乗るACノイズレベル

以前との比較では少し小さくなった気もしますが、大きな違いではないでしょう。ノイズレベルとして1mVp-p以内に収まっています。

次にDAコンバータへの設定値と出力電圧をプロットしてみました。出力レンジは12ビットに対して0-5Vです。

測定に使用したテスタはキチンと校正に出していないので参考程度にしかならないですが、DC電圧なら何十mVもズレることはまず無いので、

全くの無意味にもならないでしょう。

設定値 出力電圧(mV) 目標値(mV)

0 0(-0.2mV) 0 テスタの測定レンジを1ランク上げて0.1mV単位での測定値が-0.2mV

0x800(50%) 2.503 2.500

0xc00(75%) 3.755 3.750

0xFFF(100%) 5.00 5.000 テスタが一つ下の分解能のレンジに移動したため1mV単位での計測ができていない

この結果はかなり良い結果です。ゲインが僅かに違っていますが、この程度の差は測定器側の精度範囲内です。

最終的には精度の保障された測定器で計測する必要がありますが、それを行うに足りるだけの結果といえます。

最後に設定値を+1ずつ増やして出力電圧が追従するかどうかを確認します。

設定値 出力電圧(mV) 目標値(mV)

0x800 2.503 2.500

0x801 2.504 2.501

0x802 2.506 2.502

0x803 2.507 2.504

0x804 2.508 2.505

0x805 2.509 2.506

0x806 2.511 2.507

0x807 2.512 2.508

0x808 2.513 2.510

0x809 2.514 2.511

0x810 2.516 2.512

これもほぼ期待通りの結果です。設定値1あたり1.22mVなので設定値5おきに+2される場所が出てくることになります。

一部前後していますが全体として素直な直線性といって良い結果です。

これらの結果を総合すると12ビットのDAコンバータの性能を十分に引き出せていると言えます。

次はAD変換基板の実装と初期評価です。