スパイス 組み込み制御装置の受注製作

小規模組み込み装置に向いたCPLD

平成26年9月 6日

CPLDの持つIO機能

CPLD製品の種類はそれ程多くはないのですが、それらの中からどの製品を選択するかの選択を考えた場合、特にIOバッファ部分での機能が気になります。CPLDを使うことで従来は複数のICで実装していた論理回路の大半をCPLDに集約することが出来ます。

更に周辺回路で必要になるプルアップ抵抗やシュミットトリガ入力機能なども取り込むことが出来れば、基板上の部品点数を大きく削減できます。

ここまでは良いことを書いてきましたが、使い方を誤らないための注意点を書いておきます。

シュミットトリガ入力のヒステリシス幅は保障値がない。

ザイリンクス・アルテラ共に標準値のみ記載され、最小値・最大値の規定はありません。あまり極端な波形を入力するのは避けたほうが良い。

プルアップ抵抗のバラつきには注意が必要

通常はあまり気にしなくても良いのですが、最小値と最大値では数倍の差があります。

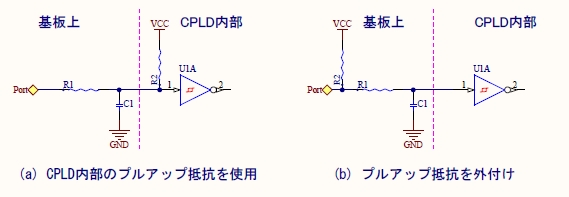

CRによるノイズフィルタを使用する場合には、使用できるRの値に上限があることに注意

CPLDにヒステリシス機能があるので、その入力段にCRによるノイズフィルタ(積分回路)をおくことで入力信号の余計なノイズを取り去ることが出来ます。このような使い方をするのは大半がIO部分です。IO部分では入力信号がない(コネクタが接続されていない)状態でも入力を安定させるために、下図のようにプルアップ抵抗を追加します。このプルアップ抵抗としてCPLD内部の抵抗を使用する場合には、上記抵抗値のバラつきが問題になります。MAXⅡを例にとるとプルアップ抵抗の最小値は5kΩです(3.3V電圧時)。入力電圧がLowのとき正しく認識されるためには入力部の抵抗R1の値はプルアップ抵抗R2の値の1/3以下でないと入力電圧の仕様を満たせません。実際にはマージンを確保する必要がありますから、このケースでの実用的なR1の値は1kΩ程度になります。

Cの値もある程度の精度(温度。使用電圧などの影響を考慮が必要)を確保するなら、それ程大きな値は取れません。比較的安価なのは0.1uF以下の値になります。これからCRの時定数の取りえる値は100uSec程度が最大になります。もしこれより大きな時定数を取りたいならプルアップ抵抗はCPLDに外付けしてもっと大きな抵抗値を使用する必要が出てきます。

(H26年9月7日追記変更)

言葉足らずでした。基板上の部品数を減らしたいなら(a)図のような接続が可能です。この接続方法の欠点は、上記で説明したように使用できる抵抗R1の値がCPLDの内部プルアップ抵抗R2によって制限される点です。外付けのプルアップ抵抗を使用するなら(b)図のように配置することで、プルアップ抵抗R2の値によらず抵抗R1の値を決定することが出来ます。

(H26年9月7日追記変更ここまで)

スルーレート制御によってダンピング抵抗を削除出来ない

ザイリンクス・アルテラ共に出力信号のスルーレート(信号変化の速さ)を2段階に調整する機能があります。この機能があればクロックやストローブ系の信号にダンピング抵抗を入れなくても波形の暴れを抑えられると期待したのですが、どうも無理そうです。どちらの製品も波形の変化量はごくわずかで帯域400MHzのオシロでは、スルーレートの違いを確認できません。配線長が数cmなら問題ないですが、ある程度長くなる配線には抵抗を挿入できるようにしておく必要があります。